Hi

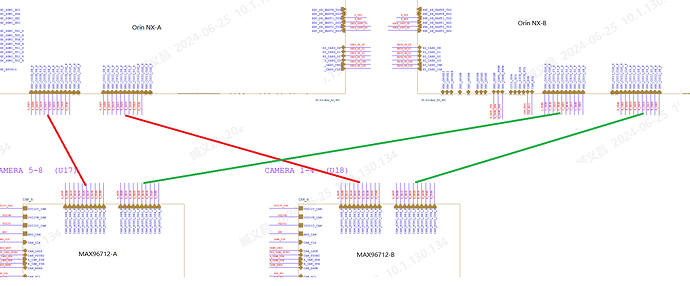

we are now adapt GMSL2 camera on Orin NX 16G, Jetpack5.1.2. Found camera data end-to-end delay about 150ms (Sensor–>GMSL2–>VI–>VIC–>EGL) . I found There are 3 parts:

- Camera signal process delay about 68ms, got from camera producter;

- VI consume about 32 ms, got by eof_timestamp - sof_timestamp;

diff kernel/nvidia/drivers/media/platform/tegra/camera/vi/vi5_fops.c /data/base/kernel/nvidia/drivers/media/platform/tegra/camera/vi/vi5_fops.c

33,34d32

< extern u64 curr_clocksource_get_offset_ns(void);

<

498,499d495

< static int cnt = 0;

<

572,577c568

< // vb->vb2_buf.timestamp = descr->status.sof_timestamp;

< vb->vb2_buf.timestamp = ktime_mono_to_real(descr->status.sof_timestamp - curr_clocksource_get_offset_ns());

<

< cnt++;

< if(0 == (cnt & 0xff))

< printk("====%lld\n****%lld\n", descr->status.sof_timestamp, descr->status.eof_timestamp);

---

> vb->vb2_buf.timestamp = descr->status.sof_timestamp;

I got the log like

[34342.218154] ====34360323961344

****34360355953792

[34355.018020] ====34373123828448

****34373155820896

[34367.817999] ====34385923806560

****34385955799072

[34380.617869] ====34398723673536

****34398755666016

[34393.417744] ====34411523540416

****34411555532928

[34406.217840] ====34424323518272

****34424355510784

[34419.017577] ====34437123384992

****34437155377440

[34431.817570] ====34449923362816

****34449955355264

- VIC consume about 37 ms, process image(3840x2160) YUYV to ARGB, crop, scalling to 1280x720.

Is it normal, is there anyway I can shorten delay for VI and VIC?