JerryChang:

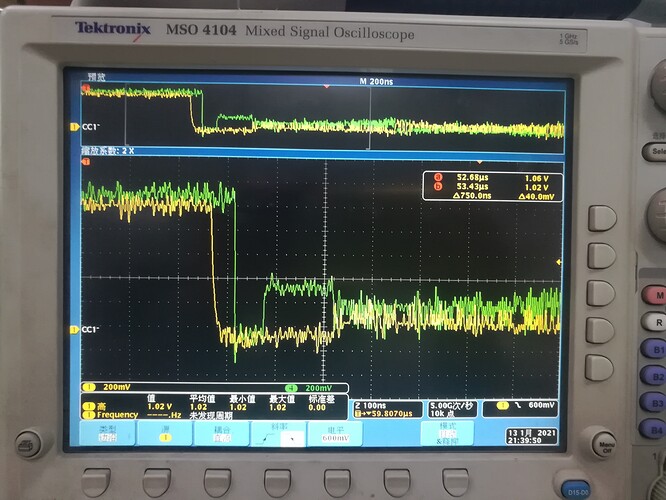

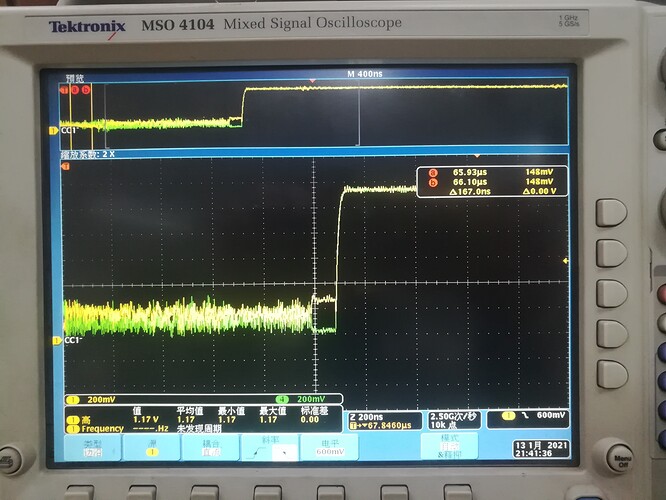

Yestoday, I measured mipi output from MAX96712 des sensor, and could not get any signal. After debugging, mipi signal could be measured on oscilloscope . And “request timed out after 2500 ms” log disappeared.

Then I got the following loop log:

[ 93.458943] tegra194-vi5 15c10000.vi: corr_err: discarding frame 0, flags: 224, err_data 4194400

[ 93.460281] tegra194-vi5 15c10000.vi: corr_err: discarding frame 0, flags: 0, err_data 16384

[ 93.492274] tegra194-vi5 15c10000.vi: corr_err: discarding frame 0, flags: 224, err_data 4194400

[ 93.525667] tegra194-vi5 15c10000.vi: corr_err: discarding frame 0, flags: 224, err_data 4194400

[ 93.526929] tegra194-vi5 15c10000.vi: corr_err: discarding frame 0, flags: 0, err_data 16384

[ 93.558944] tegra194-vi5 15c10000.vi: corr_err: discarding frame 0, flags: 224, err_data 4194400

[ 93.560258] tegra194-vi5 15c10000.vi: corr_err: discarding frame 0, flags: 0, err_data 16384

[ 93.592250] tegra194-vi5 15c10000.vi: corr_err: discarding frame 0, flags: 224, err_data 4194400

[ 93.625585] tegra194-vi5 15c10000.vi: corr_err: discarding frame 0, flags: 224, err_data 4194400

[ 93.626917] tegra194-vi5 15c10000.vi: corr_err: discarding frame 0, flags: 0, err_data 16384

[ 93.658927] tegra194-vi5 15c10000.vi: corr_err: discarding frame 0, flags: 224, err_data 4194400

The logs come from the following code:

static void vi5_capture_dequeue(struct tegra_channel *chan,

struct tegra_channel_buffer *buf)

{

int err = 0;

unsigned long flags;

struct tegra_mc_vi *vi = chan->vi;

struct vb2_v4l2_buffer *vb = &buf->buf;

struct timespec ts;

struct capture_descriptor *descr =

&chan->request[buf->capture_descr_index];

if (buf->vb2_state != VB2_BUF_STATE_ACTIVE)

goto rel_buf;

/* Dequeue a frame and check its capture status */

err = vi_capture_status(chan->tegra_vi_channel, CAPTURE_TIMEOUT_MS);

if (err) {

if (err == -ETIMEDOUT) {

dev_err(vi->dev,

"uncorr_err: request timed out after %d ms ***byd ***\n",

CAPTURE_TIMEOUT_MS);

} else {

dev_err(vi->dev, "uncorr_err: request err %d\n", err);

}

goto uncorr_err;

} else if (descr->status.status != CAPTURE_STATUS_SUCCESS) {

if ((descr->status.flags

& CAPTURE_STATUS_FLAG_CHANNEL_IN_ERROR) != 0) {

chan->queue_error = true;

dev_err(vi->dev, "uncorr_err: flags %d, err_data %d\n",

descr->status.flags, descr->status.err_data);

} else {

dev_warn(vi->dev,

"corr_err: discarding frame %d, flags: %d, "

"err_data %d\n",

descr->status.frame_id, descr->status.flags,

descr->status.err_data);

buf->vb2_state = VB2_BUF_STATE_REQUEUEING;

goto done;

}

}

… … … …

Why did these loop logs appear?