Hi,

We replace the network phy from Marvell AQR113C 10G PHY to Realtek RTL8211F-CG phy. RTL8211F-CG uses RGMII interface.

How could I let it work on our customized Orin carrier board ?

Please read the document first.

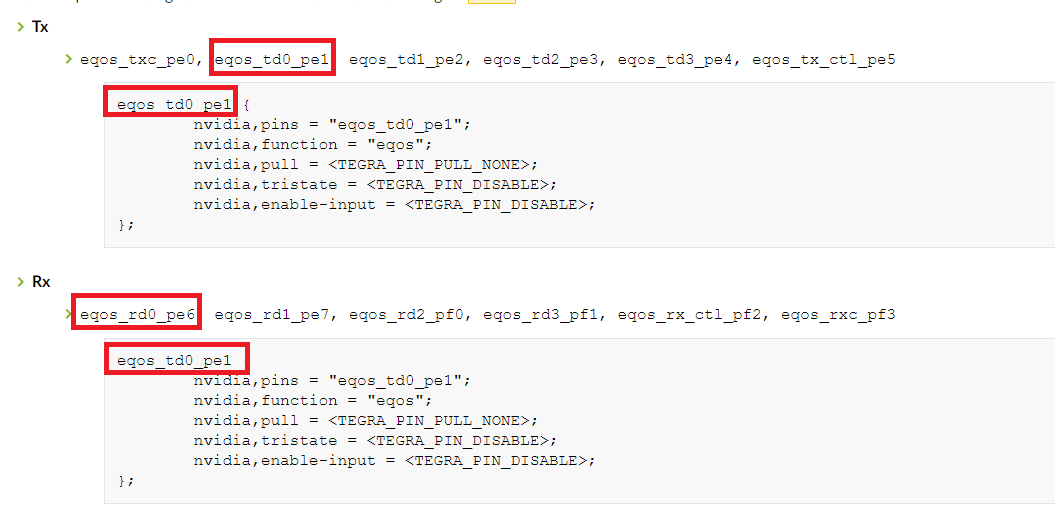

It looks the rx configuration is same as tx.

I use Jetson_AGX_Orin_Series_Pinmux_Config_Template.xlsm to generate the pinmux.dtsi, the configuration is

eqos_rd0_pe6 {

nvidia,pins = “eqos_rd0_pe6”;

nvidia,function = “eqos”;

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

Is it correct ?

Hi,

Yes,

Please try with this setup.

I reference the bring up guide to change the configurations as attached

patch_20221125_eng.zip (333.9 KB)

eth0 can be found by ifconfig, the value of RX packages changes by every ifcnofig, but the TX does not.

Can’t get the ip address by dhclient eth0.

Is there any idea or produces to debug it ?

The “nvidia,enable-input” of eqos_sma_mdio_pf4 on the web page is incorrect, but it is correct in “Adaptation_and_Bringup_for_Jetson_AGX_Orin_Deployment_Guide_DU-10991-001_06-2022.pdf.”

After changing two configurations, the phy can work correctly.

1.eqos_sma_mdio_pf4 {

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

2.nvidia,phy-rst-duration-usec = <20000>; /* usec */

It looks like website document has some problem. Let us try to update.

Thanks for the correction here.

Yes.

848145724 via NVIDIA Developer Forums <notifications@nvidia.discoursemail.com> 於 2023年3月22日 週三 下午6:16寫道:

Yes, it works on L4T R35.2.1

This topic was automatically closed 14 days after the last reply. New replies are no longer allowed.