Alright, making good progress and documenting my findings now here in case others come across this (and also for my future self).

Indeed the default mode of the pins has changed and most default to “input only” now. To use them as output, you need to adjust the DTB. Alternatively, you can write to some register. That’s what worked for me now.

Information on how to change the DTB is here: Jetson AGX Orin Platform Adaptation and Bring-Up — NVIDIA Jetson Linux Developer Guide 1 documentation

This page tells you to search for “Orin Series Pinmux” in the Jetson Download Center. However, doing so yields only one result, which is the AGX Orin one, not Nano! Searching for “nano series pinmux” gives the correct link. Note that a search just for “pin” gives a couple of pinmux results, but not the Orin Nano one. That explains why I had such a hard time finding that spreadsheet. Here is the complete link: https://developer.nvidia.com/downloads/jetson-orin-nx-and-orin-nano-series-pinmux-config-template

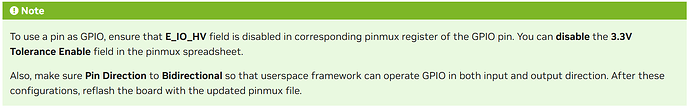

From there, you need to get hold of a copy of Microsoft Excel to use the spreadsheet, configure the pins that are supposed to be used as output, generate the dtsi files, use those to generate some more files, and eventually flash the result to the Jetson. Since I don’t have access to Microsoft Excel, I didn’t try that yet, but I suppose it would work.

Alternatively, you can write to some control register at runtime. This is “explained” here

Without this example, I would have had a very hard time finding out the address. “TRM” in point A is the Technical Reference Manual, which is then linked in point D. It’s the exact same document.

So once I had the address, I was able to read the value using busybox devmem <address>. It was always giving me 0x0000005A. The documentation says that for an input, bits 4 and 6 are set, which they indeed are in 0x0000005A. Flipping those, I get 0x0000000A. Once I had written that value to the register, I was able to use the pin as output!

Now what’s left is finding the addresses of the other pins that I need and put the busybox devmem commands in some startup script.

I agree with @bremen_matt and @tteuber in the aforementioned thread that changing the default behaviour without explicit note or a migration guide is not exactly customer friendly. On top of that we have @DaveYYY’s very inappropriate tone. Nvidia might be ahead of the competition at the moment, but once other vendors catch up, the way you treat customers will make a difference. The documentation is very much overwhelming, partly incomplete, partly outdated. If then somebody with “nvidia” next to their name calls people “dude” and treats them like little school boys that failed to read the assignment correctly, at least I will consider alternatives. That spreadsheet only working with Excel on Windows really is the icing on the cake here!