hello, I modified the hardware and powered the vdd of the sd card through gpio, and now it can sdhci3440000 is ok, but when I inserted the sd card, he prompted an error, which caused me to not be able to use the sd card normally

this is dmesgdmesg.txt (50.4 KB)

hello 984093914,

may I also know which Jetpack release you’re working with?Topic 226010 , it looks an issue with JetPack-5.0.2.

is it customize board? Jetson Xavier NX Product Design Guide for [Chapter 10.SD Card and SDIO] for reference,

you may try setting mmc-ocr-mask = <0x3>.vmmc-supply as battery_reg.

yes i have it on my own board with SDMMC_VDD_EN but it still happens, i tried to set vmmc-supply = <&hdr40_vdd_3v3>, still doesn’t work, same error

hello 984093914,

please also try configure mmc-ocr-mask, then the power up voltage depending on board capabilities can be selected.

What is mmc-ocr-mask for, let me try it

hello, i set mmc-ocr-mask=3 , but [ 80.771777] mmc1: CMD CRC or end bit error, int mask 0x40000

please have below modifications,tegra194-power-tree-p3668.dtsi

sdhci@3440000{

vmmc-supply = <&p3668_spmic_ldo3>;

vmmc-supply = <&p3668_spmic_sd2>;

}

and… for tegra194-p3668-common.dtsi

sdhci@3440000{

mmc-ocr-mask = <0x0>;

status = "okay";

}

JerryChang:

battery_reg

I changed, and then dmesg find

hello 984093914,

please refer to kernel driver for power up voltage selections.kernel_src/kernel/kernel-4.9/drivers/mmc/host/sdhci-tegra.c

static int sdhci_tegra_parse_dt(

...

if (!of_property_read_u32(np, "mmc-ocr-mask", &val)) {

if (val == 1)

host->ocr_mask &= ~(MMC_VDD_26_27 | MMC_VDD_27_28);

else if (val == 2)

host->ocr_mask &= (MMC_VDD_32_33 | MMC_VDD_165_195);

else if (val == 3)

host->ocr_mask &= (MMC_VDD_33_34 | MMC_VDD_165_195);

}

I tried to modify the value of mmc-ocr-mask, but it doesn’t work, the function still can’t be realized, when I insert the SD card, it will prompt mmc1: CMD CRC or end bit error, int mask 0x40000

Please share your board schematic.

Does this issue happen when you hotplug the card or even connect it since boot would hit this issue?

Also, please check your device tree by converting the dtb back to dts.

You won’t really know what is set in the finalized dtb file by just checking those dtsi files.

hello, this is my boardschematic

Hi,

Sorry that I am no hardware guy so may not tell it correctly. Is there any GPIO in use to control the VDD_SD_3V3?

I don’t see it in the schematic.

JerryChang:

vmmc-supply as battery_r

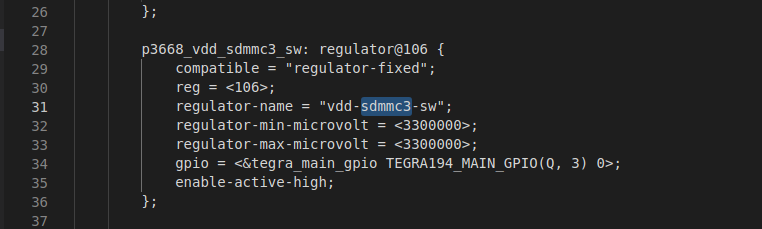

Yes, my baseboard does not have GPIO to control VDD_SD_3V3, I have another baseboard with flying wire and GPIO to control VDD_SD_3V3, I refer to other posts but set it up, but still the same problem,

Hi,

Please try with this no-gpio board first.

Add nvidia,vmmc-always-on;

You need to give a always-on regulator which is also 3.3v to the vmmc-supply. It cannot be just random dummy regulator.

hello, on this borad,i changed,but it didn’t work, this is the tree

sdhci@3440000 {

compatible = "nvidia,tegra194-sdhci";

reg = <0x0 0x3440000 0x0 0x20000>;

interrupts = <0x0 0x40 0x4>;

iommus = <0x2 0x18>;

dma-coherent;

max-clk-limit = <0xc65d400>;

bus-width = <0x4>;

cap-mmc-highspeed;

cap-sd-highspeed;

sd-uhs-sdr104;

sd-uhs-sdr50;

sd-uhs-sdr25;

sd-uhs-sdr12;

mmc-ddr-1_8v;

mmc-hs200-1_8v;

cd-inverted;

nvidia,min-tap-delay = <0x60>;

nvidia,max-tap-delay = <0x8b>;

nvidia,vqmmc-always-on;

pwrdet-support;

pinctrl-names = "sdmmc_e_33v_enable", "sdmmc_e_33v_disable";

pinctrl-0 = <0x1e>;

pinctrl-1 = <0x1f>;

ignore-pm-notify;

resets = <0x5 0x54>;

reset-names = "sdhci";

pll_source = "pll_p", "pll_c4_muxed";

nvidia,set-parent-clk;

nvidia,parent_clk_list = "pll_p", "pll_p", "pll_p", "pll_p", "pll_p", "pll_c4_muxed", "pll_c4_muxed", "pll_c4_muxed", "pll_c4_muxed", "pll_c4_muxed", "NULL";

clocks = <0x4 0x7a 0x4 0x66 0x4 0xf1 0x4 0xdb>;

clock-names = "sdmmc", "pll_p", "pll_c4_muxed", "sdmmc_legacy_tm";

uhs-mask = <0x8>;

nvidia,en-periodic-calib;

status = "okay";

vmmc-supply = <0x19>;

mmc-ocr-mask = <0x3>;

cd-gpios = <0x13 0x82 0x0>;

nvidia,cd-wakeup-capable;

nvidia,vmmc-always-on;

linux,phandle = <0xe5>;

phandle = <0xe5>;

prod-settings {

#prod-cells = <0x4>;

prod_c_1_8v {

prod = <0x0 0x1e0 0x7f00000 0x600000>;

};

prod_c_3_3v {

prod = <0x0 0x1e0 0x7f00000 0x800000>;

};

prod {

prod = <0x0 0x4 0xfff 0x200 0x0 0x28 0x22 0x2 0x0 0x100 0x1fff004a 0x5090000 0x0 0x128 0x42000000 0x0 0x0 0x1ac 0x4 0x0 0x0 0x1c0 0x1fc0 0x40 0x0 0x1c4 0x3ff77 0x400 0x0 0x1e0 0x8007f000 0x7000 0x0 0x1e4 0x20000000 0x20000000 0x0 0x204 0x80000000 0x0>;

};

prod_c_ds {

prod = <0x0 0x100 0x1fff0000 0x5090000>;

};

prod_c_hs {

prod = <0x0 0x100 0x1fff0000 0x5090000>;

};

prod_c_ddr52 {

prod = <0x0 0x3c 0x70000 0x40000 0x0 0x120 0xfffe 0x298>;

};

prod_c_hs200 {

prod = <0x0 0x3c 0x70000 0x30000 0x0 0x1c0 0xe000 0x4000>;

};

prod_c_sdr104 {

prod = <0x0 0x3c 0x70000 0x30000 0x0 0x1c0 0xe000 0x4000>;

};

prod_c_sdr12 {

prod = <0x0 0x3c 0x70000 0x0>;

};

prod_c_sdr25 {

prod = <0x0 0x3c 0x70000 0x10000>;

};

prod_c_sdr50 {

prod = <0x0 0x3c 0x70000 0x20000 0x0 0x1c0 0xe000 0x8000>;

};

};

};

tegra194-p3668-all-p3509-0000.dts (224.9 KB)

hello, this my dtsi