hello Out_of_the_BOTS,

there’s an issue to configure GPIO directly,

currently, if you would like to make changes dynamically, you may use devmem/reg_dump to update pinmux register , or update MB1 pinmux bct file.

for example,

pinmux.0x02430030 = 0x0000005a; # soc_gpio42_pq6: rsvd2, pull-up, tristate-enable, input-enable, io_high_voltage-disable, lpdr-disable

please set both bit-4 and bit-6 as 0 to configure this pin as output mode. after that, you should be able to control the pin through sysfs.

for example,

pinmux register: 0x02430030 / Default boot value: 0x5a

please update bit-4 and bit-6 to set required direction. whereas, Output: Bit 4 = 0 Bit 6=0, Input: Bit 4=1 Bit 6=1

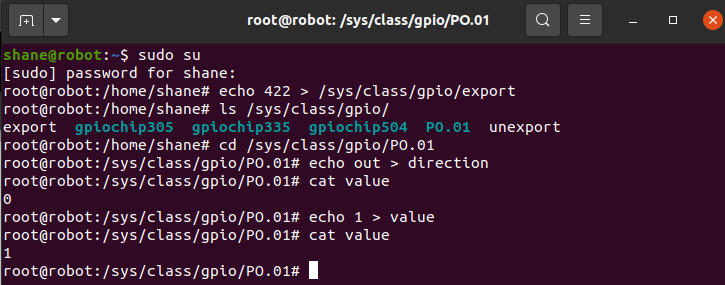

please try below steps to make GPIO output working.

$ sudo devmem2 0x02430030 w 0x0a

$ echo [GPIO number] > /sys/class/gpio/export

$ cd /sys/class/gpio/PQ.06

$ echo out > direction

$ cat value # change value and check.

BTW,

you’ll need to double check the gpio numbers. please see-also To check the GPIO number.

since I don’t have Xavier NX for double check, please examine the GPIO allocation range, you should check kernel init messages.

for example, this is the results by Orin AGX.

[ 6.007898] gpiochip0: registered GPIOs 348 to 511 on tegra234-gpio

[ 6.013957] gpiochip1: registered GPIOs 316 to 347 on tegra234-gpio-aon

furthermore,

this issue is fixed, you may expect next JetPack public release (l4t-r35.1) to include the fixes.