I add the lt6911uxc driver to I2C-8 in device tree.GPIO

[ \hardware\nvidia\platform\t19x\galen\kernel-dts\tegra194-p2888-0001-p2822-0000.dts ]

#include "common/tegra194-p2888-0001-p2822-0000-common.dtsi"

#include "common/tegra194-p2822-camera-modules.dtsi"

#include "t19x-common-modules/tegra194-camera-plugin-manager.dtsi"

#include "common/tegra194-p2822-0000-hdmi2mipi-lt6911uxc-a00.dtsi" // add FPGA driver

[ common/tegra194-p2822-0000-hdmi2mipi-lt6911uxc-a00.dtsi ]

#define LT6911_EN "okay"

/ {

/* set lt6911uxc reset and interrupt gpio direction */

gpio@2200000 {

camera-control-output-low {

status = LT6911_EN;

gpio-hog;

output-low;

gpios = <TEGRA194_MAIN_GPIO(H, 3) 0>;

label = "cam0-rst";

};

camera-control-input {

status = LT6911_EN;

gpio-hog;

input;

gpios = <TEGRA194_MAIN_GPIO(P, 0) 0>;

label = "cam0-int";

};

};

/* i2c-8 */

i2c@31e0000 {

clock-frequency = <100000>;

lt6911uxc_a@2b {

compatible = "lontium,lt6911uxc";

reg = <0x2b>;

status = LT6911_EN;

devnode = "video0";

/* Reset */

reset-gpio = <&tegra_main_gpio TEGRA194_MAIN_GPIO(H, 3) GPIO_ACTIVE_HIGH>;

/* Interrupt */

interrupt-parent = <&tegra_main_gpio>;

interrupts = <TEGRA194_MAIN_GPIO(P, 0) IRQ_TYPE_LEVEL_HIGH>;

port@0 {

ret = <0>;

status = LT6911_EN;

hdmi2csi_lt6911_out0:

endpoint {

status = LT6911_EN;

port-index = <0>;

bus-width = <4>;

remote-endpoint = <&hdmi2csi_csi_in0>;

};

};

};

};

}

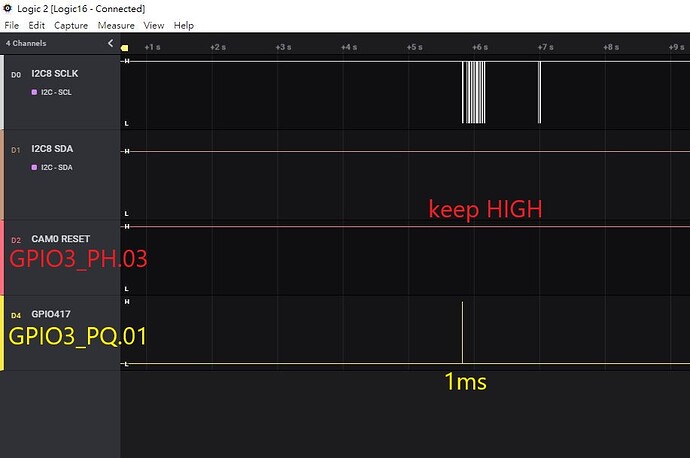

I pull cam0-rst(pin L5, GPIO3_PH.03) to HIGH in lt6911uxc_probe, and read lt6911uxc chip id by I2C-8.

[ \kernel\nvidia\drivers\media\i2c\lt6911uxc.c ]

static int lt6911uxc_probe(struct i2c_client *client, const struct i2c_device_id *id)

{

struct lt6911uxc_state *state;

struct v4l2_subdev *sd;

int err = 0;

dev_info(&client->dev, "Probing lt6911uxc\n");

state = devm_kzalloc(&client->dev, sizeof(struct lt6911uxc_state), GFP_KERNEL);

if (!state)

return -ENOMEM;

state->pdata = lt6911uxc_parse_dt(client);

if (!state->pdata)

return -ENODEV;

state->i2c_client = client;

sd = &state->sd;

v4l2_i2c_subdev_init(sd, client, <6911uxc_ops);

dev_info(&client->dev, "Chip found @ 7h%02X (%s)\n", client->addr, client->adapter->name);

// Release CAM_RST Reset (pin L5, GPIO3_PH.03)

dev_info(&client->dev, "Releasing CAM_RST Reset (gpio 0x%04X)\n", state->pdata->reset_gpio);

if (!gpio_is_valid(state->pdata->reset_gpio))

{

dev_err(&client->dev, "Reset CAM_RST GPIO is invalid!\n");

return state->pdata->reset_gpio;

}

err = devm_gpio_request_one(&client->dev, state->pdata->reset_gpio, GPIOF_OUT_INIT_HIGH, "lt6911uxc-reset");

if (err)

{

dev_err(&client->dev, "Failed to request Reset CAM_RST GPIO 0x%04X: %d\n",

state->pdata->reset_gpio, err);

return err;

}

// CAM0_RST Reset (pin L5, GPIO3_PH.03)

gpio_set_value(state->pdata->reset_gpio, 0);

usleep_range(30, 50);

dev_info(&client->dev, "CAM0_RST Reset (gpio 0x%04X) to low\n", state->pdata->reset_gpio);

gpio_set_value(state->pdata->reset_gpio, 1);

usleep_range(30, 50);

dev_info(&client->dev, "CAM0_RST Reset (gpio 0x%04X) to high\n", state->pdata->reset_gpio);

/* read CHIP ID */

lt6911uxc_read_chipid(sd);

/* initial setup */

lt6911uxc_initial_setup(state);

return 0;

err_ctrl_handler:

v4l2_ctrl_handler_free(&state->ctrl_handler);

return err;

}

static struct lt6911uxc_platform_data* lt6911uxc_parse_dt(struct i2c_client *client)

{

struct device_node *node = client->dev.of_node;

struct lt6911uxc_platform_data *pdata;

const struct of_device_id *match;

int gpio;

dev_dbg(&client->dev, "%s \n", __func__);

match = of_match_device(lt6911uxc_of_match, &client->dev);

if (!match)

{

dev_err(&client->dev,

"Driver has not been loaded from an of_match\n");

return NULL;

}

pdata = devm_kzalloc(&client->dev,sizeof(struct lt6911uxc_platform_data), GFP_KERNEL);

gpio = of_get_named_gpio(node, "reset-gpio", 0);

if(gpio < 0)

{

if(gpio == -EPROBE_DEFER)

{

dev_err(&client->dev, "reset-gpio read failed: (%d)\n", gpio);

goto prop_err;

}

dev_info(&client->dev, "reset-gpio not found, ignoring\n");

}

pdata->reset_gpio = gpio;

return pdata;

prop_err:

dev_err(&client->dev, "Could not parse DT parameters\n");

devm_kfree(&client->dev, pdata);

return NULL;

}

I see the cam0-rst(pin L5, GPIO3_PH.03) keep to LOW in lt6911uxc_probe(), but I had set the GPIO3_PH.03 to HIGH and it seem doesn’t work, so it wil get i2c8 read fail.

gpio_set_value(state->pdata->reset_gpio, 1);

How to check the other driver hold CAM0-RESET(GPIO3_PH.03) to LOW?

Why I can not pull CAM0-RESET(GPIO3_PH.03) to HIGH in my lt6911uxc_probe()?