Please provide the following info (tick the boxes after creating this topic):

Software Version

DRIVE OS 6.0.8.1

DRIVE OS 6.0.6

DRIVE OS 6.0.5

DRIVE OS 6.0.4 (rev. 1)

DRIVE OS 6.0.4 SDK

other

Target Operating System

Linux

QNX

other

Hardware Platform

DRIVE AGX Orin Developer Kit (940-63710-0010-300)

DRIVE AGX Orin Developer Kit (940-63710-0010-200)

DRIVE AGX Orin Developer Kit (940-63710-0010-100)

DRIVE AGX Orin Developer Kit (940-63710-0010-D00)

DRIVE AGX Orin Developer Kit (940-63710-0010-C00)

DRIVE AGX Orin Developer Kit (not sure its number)

other

SDK Manager Version

1.9.3.10904

other

Host Machine Version

native Ubuntu Linux 20.04 Host installed with SDK Manager

native Ubuntu Linux 20.04 Host installed with DRIVE OS Docker Containers

native Ubuntu Linux 18.04 Host installed with DRIVE OS Docker Containers

other

Hello,

I am experimenting with fsync-groups with the TSC generator and NVPPS and while I am getting encouraging results, the most important part seems to not be working as implied by the Orin Timesync document. Specifically:

- I enabled fsync-groups in the dtsi, changing from status=“disabled” to status=“okay”

- I have an external PTP master connected to J11 Port 4, and ptp4l is running on mgbe2_0 and shows a valid synchronization

- I use ioctl to poke nvpps (timer mode, results in nanoseconds) to get the both tsc and ptp timestamps of the last event, both are showing reasonable values

- I use the offset value from the ptp timestamp to the tsc timestamp, modulo 1 second, converted down to tsc ticks and use nvsipl_camera with the -F flag (fsync-groups), specifying group 0 and the tsc tick count of the desired time of start triggering (plus something like 2 seconds to let it initialize first)

- I am probing the output of the camera trigger and comparing it to the PPS output of my PTP grandmaster

I would expect based on the documentation that I have effectively told it ‘start at the TSC equivalent of the PTP second’, and I would expect that the rising edge of the trigger would concide with the PPS output of the grandmaster plus or minus the lock-in value (by default 20us) of the TSC to PTP synchronization system.

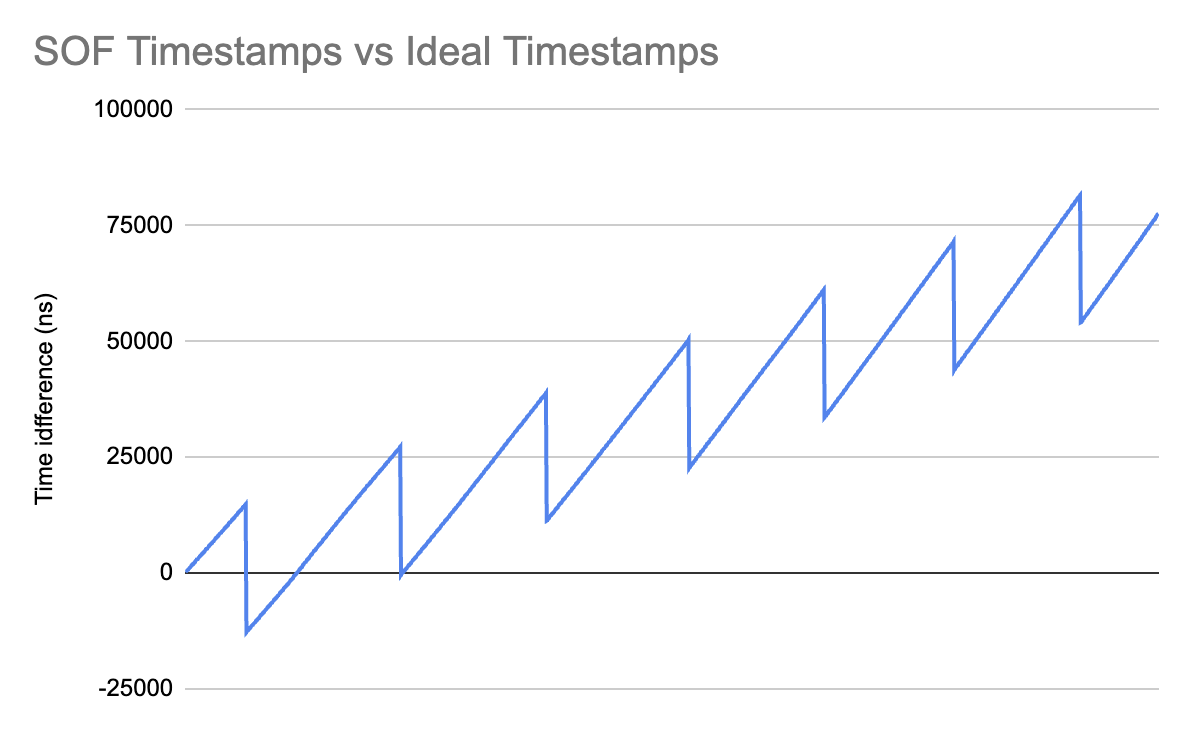

Instead, I see the rising edges start nearly perfectly aligned every time (off by about 2 microseconds), and then the fsync pulse starts moving backwards relative to grandmaster PPS output, sliding continuously at the rate of a few microseconds per second, until it’s well over 20 microseconds.

This tells me that whatever mechanism is aligning TSC and PTP is not working accurately. I can verify (1) that the ptp4l instance is working correctly and that I am timesync’d to the external grandmaster, (2), dmesg tells me that it is getting lock state updates, and while it does say that it can’t get concurrent timestamps from mgbe2_0, it appears that it is in fact working correctly (I suspect that is when I was starting ptp4l on mgbe2_0, and (3) the fsync groups are working as expected, though I note that I have to rmmod and modprobe cam_fsync every time as nvsipl_camera doesn’t appear to cleanly disable cam_fsync after it quits. Here’s the dmesg output for nvpps:

timestamps [ 1.386912] nvpps c6a0104.nvpps: nvpps_probe

[ 1.386921] nvpps c6a0104.nvpps: PPS GPIO not provided in DT, only Timer mode available

[ 1.386923] nvpps c6a0104.nvpps: using ptp notifier method with interface(mgbe2_0)

[ 1.386925] nvpps c6a0104.nvpps: tsc_res_ns(32)

[ 1.387024] nvpps c6a0104.nvpps: nvpps cdev(509:0)

[ 1.387155] nvpps c6a0104.nvpps: tegra_gte_register_event err = -22

[ 1.387170] nvpps c6a0104.nvpps: TSC config ptx 0x313

[ 10.591468] nvpps nvpps0: tsc_lock_stat:25

[ 12.639477] nvpps nvpps0: tsc_lock_stat:45

[ 3636.575468] nvpps nvpps0: tsc_lock_stat:c5

[ 3637.599469] nvpps nvpps0: tsc_lock_stat:e5

[ 3656.065262] nvpps nvpps0: failed to get PTP_TSC concurrent timestamp from interface(mgbe2_0)

[10444.127463] nvpps nvpps0: tsc_lock_stat:45

[10446.175462] nvpps nvpps0: tsc_lock_stat:65

[10448.223462] nvpps nvpps0: tsc_lock_stat:85

[10450.271478] nvpps nvpps0: tsc_lock_stat:a5

[10452.319471] nvpps nvpps0: tsc_lock_stat:c5

[11225.439395] nvpps nvpps0: tsc_lock_stat:15

[11227.487391] nvpps nvpps0: tsc_lock_stat:35

[11232.607388] nvpps nvpps0: tsc_lock_stat:95

[11243.871387] nvpps nvpps0: tsc_lock_stat:45

[11279.711375] nvpps nvpps0: tsc_lock_stat:85

[11281.759380] nvpps nvpps0: tsc_lock_stat:a5

Can you please help me out to figure out why PPS to TSC syntonization isn’t working as described in the documentation?