We do not use ORIN’s original XFI bus and Mask it in pinmux.dtsi.

We use the 88E1510 driver,RGMII, MDIO, MDC, reset,int are enabled in pingmux.dtsi, and their definitions are also added in gpio.dtsi.

Eth0 can be seen in the system, and can be up and down, but after the eth0 up and down, no interrupt trigger can be seen in the log.

After the network cable is inserted, it also shows that it is not connected,so we checked the circuit from PHY to cooper,we think the circuit is correct.

Can you give some suggestions on the circuit and software configuration from ORIN to PHY?

rgmii_ethernet.tar.gz (15.9 KB)

This is the schematic diagram of our network

orin_a01.pdf (228.3 KB)

Thanks

If interrupt is not showing up, it means your pinmux or device tree is still wrong.

What did you change in your device tree? Are you sure these pinmux change and device tree change are flashed to the board correctly?

please refer to the document from this.

We modified pingmux and gpio according to our own hardware design. It can successfully enter the system and display, so the modified pinmux should be successfully burned in.But what does device tree mean?Which file is device tree

This is a dts file converted from dtb(rootfs/boot/Tegra234-p3701-0000-p3737-0000.dtb

a.dts (492.9 KB)

). Would you please check it for any problems?

No, please check it by yourself. The document is already there.

Also, make sure the device tree you flash to the board is really the one you modified. You can learn to check that by reading your own flash log.

Also, put the device tree into kernel/dtb in your Linux_for_Tegra folder.

Have you measured the ENET_INT pin to check if it is pulled to low when cable inserted?

I want to confirm whether the ENET pin is ORIN to phy or PHY to orin.Because some engineers in the forum configured it as input, the xavier development suite looks like enet_ Int is the output pin. thx

It is from PHY to Orin. Have you measured it?

When the network cable is inserted, ENET_ Int is not pulled down

Then it looks more like the PHY issue. Have you checked your PHY setting/datasheet/design to find out why there is no INT output?

Hi Trumany, thanks for your help.

Yesterday I added several print codes in phy config entry, like printk, phydev_warn, dev_err, but I didn’t see any one output in dmesg, seems the phy chip didn’t initialize, what can cause this?

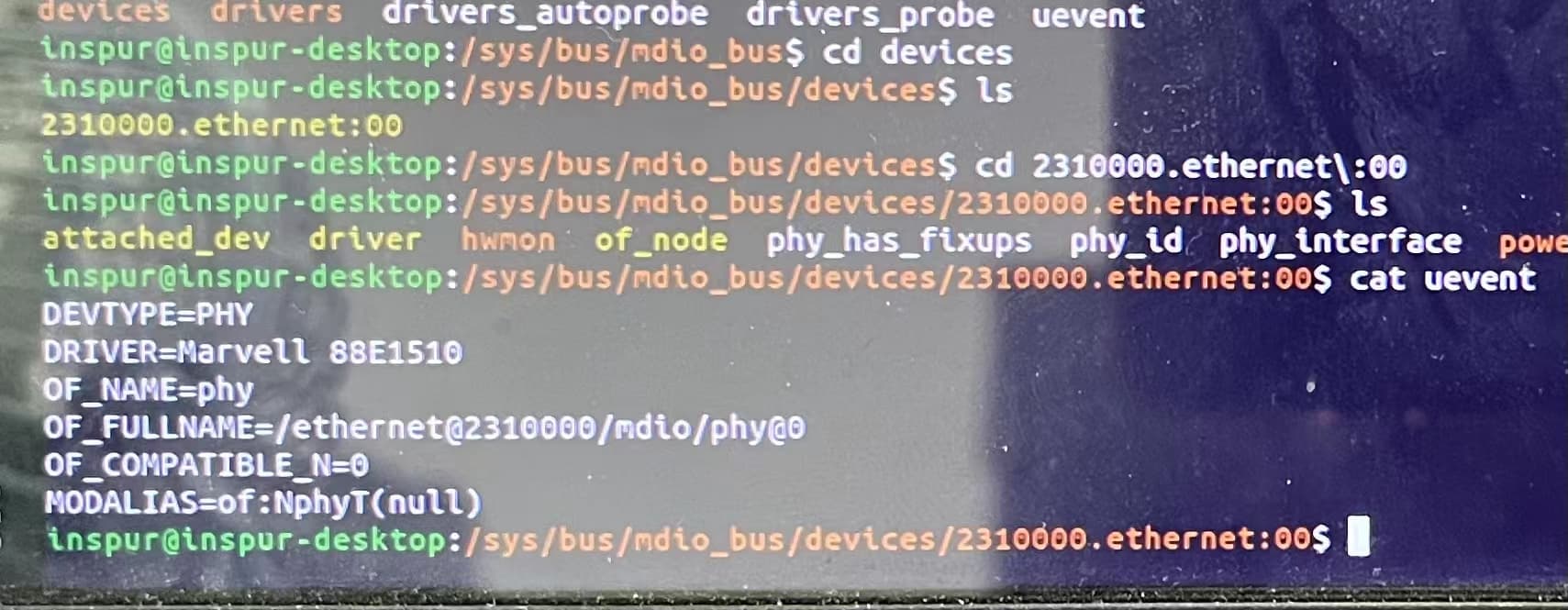

Please check if the driver under your mdio bus really matches to the phy driver you are using.

I copied the new Image to Linux_for Tegra/kernel and Linux_for_Tegra/rootfs/boot;Copied tegra234-p3701-0000-p3737-0000.dtb and tegra234-p3701-0004-p3737-0000.dtb to rootfs/boot and kernel/dtb

Could you clarify why you said your pinmux is different from the guide from our document? Did you really read our document?

I mean only for the RGMII part.

also, please check if the 88E1512 reset pin is toggled or not. If this pin is always in reset state, then PHY won’t work.

reset pin works, but int never triggered

/* SFIO Pin Configuration */

pinmux_default: common {

/* Add for rgmii eth */

eqos_txc_pe0 {

nvidia,pins = “eqos_txc_pe0”;

nvidia,function = “eqos”;

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

eqos_td0_pe1 {

nvidia,pins = "eqos_td0_pe1";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

eqos_td1_pe2 {

nvidia,pins = "eqos_td1_pe2";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

eqos_td2_pe3 {

nvidia,pins = "eqos_td2_pe3";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

eqos_td3_pe4 {

nvidia,pins = "eqos_td3_pe4";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

eqos_tx_ctl_pe5 {

nvidia,pins = "eqos_tx_ctl_pe5";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

eqos_rd0_pe6 {

nvidia,pins = "eqos_rd0_pe6";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_rd1_pe7 {

nvidia,pins = "eqos_rd1_pe7";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_rd2_pf0 {

nvidia,pins = "eqos_rd2_pf0";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_rd3_pf1 {

nvidia,pins = "eqos_rd3_pf1";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_rx_ctl_pf2 {

nvidia,pins = "eqos_rx_ctl_pf2";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_rxc_pf3 {

nvidia,pins = "eqos_rxc_pf3";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_sma_mdio_pf4 {

nvidia,pins = "eqos_sma_mdio_pf4";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

};

eqos_sma_mdc_pf5 {

nvidia,pins = "eqos_sma_mdc_pf5";

nvidia,function = "eqos";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

};

/add end/

and removed pg4/5 from unused lowpower, add to here:

/* GPIO Pin Configuration */

/add for rgmii eth/

soc_gpio17_pg4 {

nvidia,pins = “soc_gpio17_pg4”;

nvidia,function = “rsvd0”;

nvidia,pull = <TEGRA_PIN_PULL_UP>;

nvidia,tristate = <TEGRA_PIN_ENABLE>;

nvidia,enable-input = <TEGRA_PIN_ENABLE>;

nvidia,lpdr = <TEGRA_PIN_DISABLE>;

};

soc_gpio18_pg5 {

nvidia,pins = "soc_gpio18_pg5";

nvidia,function = "rsvd0";

nvidia,pull = <TEGRA_PIN_PULL_NONE>;

nvidia,tristate = <TEGRA_PIN_DISABLE>;

nvidia,enable-input = <TEGRA_PIN_DISABLE>;

nvidia,lpdr = <TEGRA_PIN_DISABLE>;

};

/add end/