Can I use Nano 2GB to connect two channels max9296, each channel max9296 to two channels max9295, each channel max9295 to one IMX490 with ISP?

The first is a wiring diagram of nano 2GB, and the second is a wiring diagram of 9296。

Since nano2GB’s CSI0 /1/2/3 are 2 pairs of Lane, each MAX9296 portA and portB connects only 2 pairs of Lane to a CSIx of nano2GB.

The output image format of each IMX490 camera is 2880*1860@30fps YUV422-8bit.

When I run the v4l2-ctl command, the following error occurs: video4linux video0: frame start syncpt timeout!0dmesg_log.txt (63.8 KB)imx490.c (49.5 KB)imx490_mode_tbls.h (11.1 KB)tegra210-camera-rbpcv2-imx490.dtsi (28.8 KB)tegra210-porg-camera-rbpcv2-imx490.dtsi (4.0 KB)

After I use this command: echo 7 >/sys/class/video4linux/video0/dev_debug I then use the v4l2-ctl --set-fmt-video=width=2880,height=1680,pixelformat=YUYV --set-ctrl bypass_mode=0 --stream-mmap --stream-count=100 -d /dev/video0 --stream-to=ov491.raw command and generate a new logdmesg_log1.txt (7.3 KB)

Enable the debug print in csi2_fops.c to check the error log to analysys.

hi ShaneCCC

Check below command.

sudo su

echo file csi2_fops.c +p > /sys/kernel/debug/dynamic_debug/control

hi ShaneCCC

nvidia@nvidia-desktop:~$ sudo su

[ 784.370250] vi 54080000.vi: Calibrate csi port 2

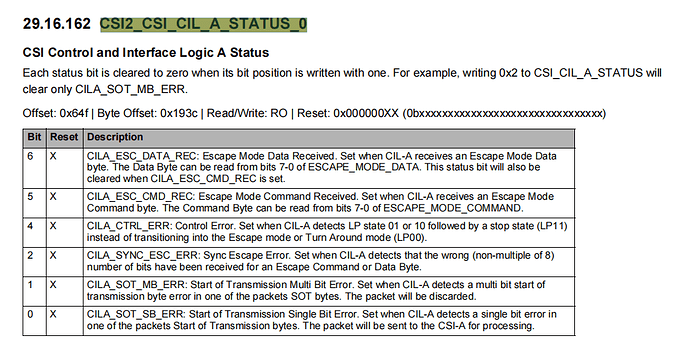

Looks like signal problem. Have check the REG CSIx_CSI_CILA_STATUS_0 from TRM to get more information.

CILA_CTRL_ERR: Control Error. Set when CIL-A detects LP state 01 or 10 followed by a stop state (LP11)

instead of transitioning into the Escape mode or Turn Around mode (LP00).

Hi ShaneCCC

?

I refer to this document, and I get confused.

I know .But it juest print

vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 383.915704] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 383.915719] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 383.915854] vi 54080000.vi: cil_settingtime was autocalculated

[ 383.915873] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 384.117432] video4linux video0: frame start syncpt timeout!0

[ 384.123789] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[…

I want to debug a camera first.

the csi2 is 2 lanes

In my dtsi configuration

port-index = <2>;

Is this the right configuration?

[tegra210-camera-rbpcv2-imx490.dtsi|attachment](upload://uqQc4oKDqlAb91uDkE6Vjrc6yVl.dtsi) (28.8 KB)

The port-index/bus-width … in device tree is correct.Tegra X1 SoC Technical Reference Manual

ShaneCCC:

CSIx_CSI_CILA_STATUS_0

vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040040

[ 113.837690] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

0x00000010 == 0b00010000

This message shows that Bit 4 is set to 1 . means CILA_CTRL_ERR

[ 113.837737] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040040

Hi Shane

Sorry, may need to check with scope to make sure the signal.

system

March 9, 2022, 2:00am

19

This topic was automatically closed 14 days after the last reply. New replies are no longer allowed.