my custom board replace sensor with 2 4-lane sensor(csi2/3 and csi4). how should i edit the dts files?

i use tegra210-p3448-0000-p3449-0000-b00.dts.

the port-index shouild be 2 and 4? and bus-width should be 4?

and the i2c i use cam_i2c and i2c2, how can i adapt it? my custom board remove the cam_mux_sel

Have check this doc.

what aboat the i2c port?

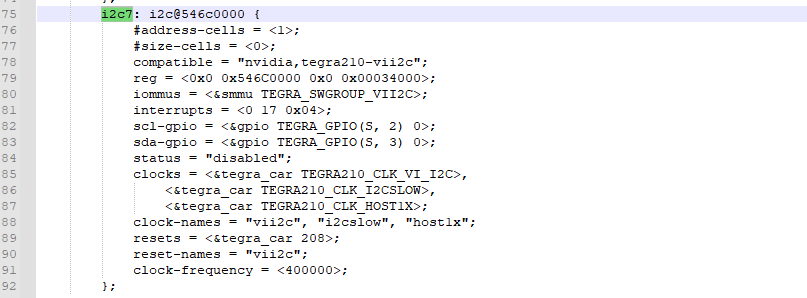

Have a reference to the reference sensor board like below define the sensor below the i2c@546c0000

host1x {

27 i2c@546c0000 {

28 ov5693_c@36 {

29 /* Define any required hw resources needed by driver */

30 /* ie. clocks, io pins, power sources */

31 /* mclk-index indicates the index of the */

32 /* mclk-name with in the clock-names array */

33

34 clocks = <&tegra_car TEGRA210_CLK_CLK_OUT_3>;

35 clock-names = "clk_out_3";

Hi, ShaneCCC

my mclk have no signal,how can i fix it?

Add some message to below file to check if it set properly.

./camera/camera_common.c: err = of_property_read_string(np, “mclk”, &pdata->mclk_name);

Because of the imx219’s dts-file have not label mclk.

so should i insert the label to there? and what’s the value should be?

host1x {

i2c@546c0000 {

rbpcv2_imx219_a@36 {

status = “disabled”;

clocks = <&tegra_car TEGRA210_CLK_CLK_OUT_3>;

clock-names = “clk_out_3”;

clock-frequency = <24000000>;

mclk = “clk_out_3”;

reset-gpios = <&gpio CAM1_PWDN GPIO_ACTIVE_HIGH>;

};

};

};

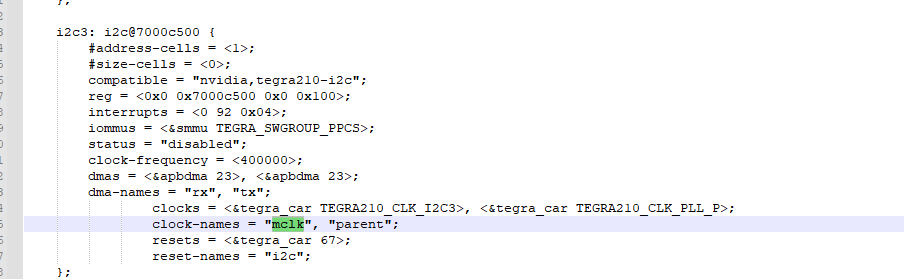

i2c@7000c500 {

rbpcv2_imx219_e@36 {

status = "disabled";

clocks = <&tegra_car TEGRA210_CLK_CLK_OUT_3>;

clock-names = "clk_out_3";

clock-frequency = <24000000>;

mclk = "clk_out_3";

reset-gpios = <&gpio CAM2_PWDN GPIO_ACTIVE_HIGH>;

};

};

i add label mclk clocks and so on. and mclk has signal. but mipi no data. how can i get the log of mipi,that i can confirm the sensor is init ok (i can get/set sensor register).

the b01 camera0/camera1 use csi0/2, but the label port-index of dts-file is 0/4. so if camera0/camera1 use csi2/4, the label port-index of dts-file will be 4/8?

The port-index is the same with csi number, csi0 then port-index=0

hi ShaneCCC, how can i get the log of mipi data?

You can enable the dev_dbg() in csi2_fops.c to print the status for checked.

[ 4899.146317] video4linux video1: frame start syncpt timeout!0

[ 4899.152509] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4899.152526] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4899.152542] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4899.152663] vi 54080000.vi: cil_settingtime was autocalculated

[ 4899.152682] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 4899.354060] video4linux video1: frame start syncpt timeout!0

[ 4899.360308] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4899.360326] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4899.360342] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4899.360432] vi 54080000.vi: cil_settingtime was autocalculated

[ 4899.360450] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 4899.562367] video4linux video1: frame start syncpt timeout!0

[ 4899.568723] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4899.568740] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4899.568755] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4899.568846] vi 54080000.vi: cil_settingtime was autocalculated

[ 4899.568864] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 4899.770343] video4linux video1: frame start syncpt timeout!0

[ 4899.776617] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4899.776634] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4899.776649] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4899.776770] vi 54080000.vi: cil_settingtime was autocalculated

[ 4899.776788] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 4899.978184] video4linux video1: frame start syncpt timeout!0

[ 4899.984503] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4899.984521] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4899.984536] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4899.984674] vi 54080000.vi: cil_settingtime was autocalculated

[ 4899.984694] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 4900.186298] video4linux video1: frame start syncpt timeout!0

[ 4900.192553] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4900.192570] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4900.192586] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4900.192713] vi 54080000.vi: cil_settingtime was autocalculated

[ 4900.192732] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 4900.394308] video4linux video1: frame start syncpt timeout!0

[ 4900.400594] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4900.400611] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4900.400627] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4900.400756] vi 54080000.vi: cil_settingtime was autocalculated

[ 4900.400774] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 4900.602020] video4linux video1: frame start syncpt timeout!0

[ 4900.609185] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4900.609204] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4900.609221] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4900.609355] vi 54080000.vi: cil_settingtime was autocalculated

[ 4900.609373] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 4900.810296] video4linux video1: frame start syncpt timeout!0

[ 4900.816486] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4900.816504] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4900.816520] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4900.816645] vi 54080000.vi: cil_settingtime was autocalculated

[ 4900.816664] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 4901.018145] video4linux video1: frame start syncpt timeout!0

[ 4901.024232] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4901.024243] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4901.024254] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4901.024330] vi 54080000.vi: cil_settingtime was autocalculated

[ 4901.024343] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 4901.226073] video4linux video1: frame start syncpt timeout!0

[ 4901.232020] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4901.232032] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4901.232044] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4901.232128] vi 54080000.vi: cil_settingtime was autocalculated

[ 4901.232140] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 4901.434332] video4linux video1: frame start syncpt timeout!0

[ 4901.440474] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4901.440528] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4901.440578] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4901.440794] vi 54080000.vi: cil_settingtime was autocalculated

[ 4901.440815] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 4901.642269] video4linux video1: frame start syncpt timeout!0

[ 4901.648376] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4901.648397] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4901.648415] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4901.648504] vi 54080000.vi: cil_settingtime was autocalculated

[ 4901.648523] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

[ 4901.850133] video4linux video1: frame start syncpt timeout!0

[ 4901.856032] vi 54080000.vi: TEGRA_CSI_PIXEL_PARSER_STATUS 0x00000000

[ 4901.856042] vi 54080000.vi: TEGRA_CSI_CIL_STATUS 0x00000010

[ 4901.856050] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

[ 4901.856106] vi 54080000.vi: cil_settingtime was autocalculated

[ 4901.856114] vi 54080000.vi: csi clock settle time: 13, cil settle time: 10

i use v4l2-demo and the log.

the demo stuck in VIDIOC_DQBUF.

Below error tell the clock/data lane control error have a check the REG CSI_CSI_CILA_STATUS_0 and CSI_CSI_CIL_A_STATUS_0 from the TRM.

It could be the sensor with continous clock mode and enable sensor streaming before enable NVCSI.

[ 4901.856050] vi 54080000.vi: TEGRA_CSI_CILX_STATUS 0x00040041

hi shane, so is it REG issue?

hi shane, where can i get the doc of REG?

hi shane,

what’s the diffrent of csi4_fops.c and csi2_xxxx.c?