Hello,

I’m working with the Osbourn board using the Orin AGX 32G and have encountered some unexpected behavior related to UPHY configuration. I’m using the latest NVIDIA SDK (Jetpack 6.2, L4T 36.4.3) and referencing the Jetson AGX Orin Design Guide v1.7 (DG-10653-001) for PHY configurations.

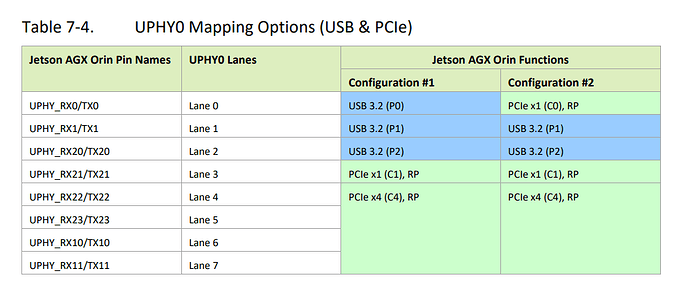

UPHY0:

-

The USB3.2 (P0) port on lan0 only functions as USB 2.0. I have configured it using Configuration #1 from the design guide, which should enable USB 3.0.

-

File: p3701.conf.common:

Configuration Used: ODMDATA="gbe-uphy-config-22,hsstp-lane-map-3,nvhs-uphy-config-0,hsio-uphy-config-0,gbe0-enable-10g";

Above is the table from the Jetson-AGX-Orin-Design-Guide_DG-10653-001v1.7

UPHY1:

No issues observed.

UPHY3:

I tested both the MGBE interface (Lane #6) and Minicard (PCIe via Lane #0), and both work simultaneously. While this is great, it’s unexpected based on the restrictions outlined in the v1.7 Design Guide, where this combination shouldn’t be valid.

Above is the table from Jetson-AGX-Orin-Design-Guide_DG-10653-001v1.7

Interestingly, this behavior aligns with an older version of the design guide (v0.2 – Jetson_AGX_Orin_Design_Guide_DG-10653-001_v0.2), which allowed per-PHY configuration and supports the scenario I’m seeing.

Above is that table from Jetson-AGX-Orin-Design-Guide_DG-10653-001v0.2

Note: v0.2

Queries:

-

Why does the latest SDK (Jetpack 6.2) seem to follow the behavior defined in the older v0.2 guide, rather than adhering to the latest v1.7 guide?

-

If this per-PHY configuration behavior is intentionally supported in the latest SDK, can I:

-

Enable all three USB ports with USB 3.0 support, and

-

Continue using the current UPHY2 configuration (MGBE on C0 and PCIe Minicard on C7)?

-

Please let me know if any additional information is required. I appreciate your insights and support on this. Thank you.

Regards,

Brijesh Thakkar