Hi Sir,

We have some problem on TPM, so we want check with you how we can do.

Our TPM on NX can’t initial.

Wish you can point out our mistake.

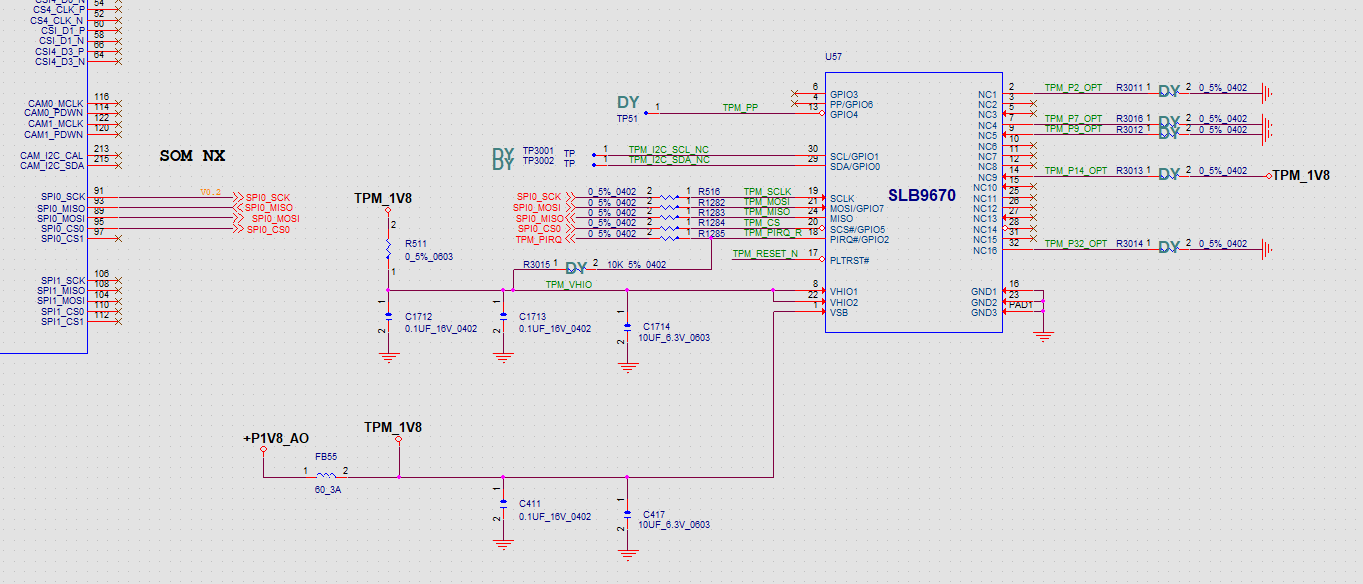

We use NX module, and TPM is SLB9670, schematic as below,

We measure waveform in initial, you can see photo as below

You can see MI and MO default is Low.

Our OS is Ubuntu.

And we use the same TPM(SLB9670) on other Linux Platform(X86, Ubuntu),

You can see MI and MO default is High.

So we have some question want to check in phenomenon:

Q1. Is our schematic need PU resistor?

PDG have no detail desciption in SPI pins.

Q2. It seems that MI and MO behavier is different on those platform,

we not sure which one is correct?

If x86 platform is correct? How can I adjust register?

Q3. X86 platfom CLK is longer than NX platform 8bit.

I not sure is it correct on NX platform. Or we have something worng?

Pin Matrix setting as below, is it correct?

If you need more detail setting, please let us know, we will provide it as soon as possible.

This problem bother us several weeks, hope we have some progress

Thanks,

Allison