ALL:

The function of our spi is ok,we can read&write data with spi interface.We just want to decrease the time be spent for a spi translation.

I have read these topics:

https://devtalk.nvidia.com/default/topic/1029410/jetson-tx1/spi-cs-issue/

https://devtalk.nvidia.com/default/topic/1037334/?comment=5270650

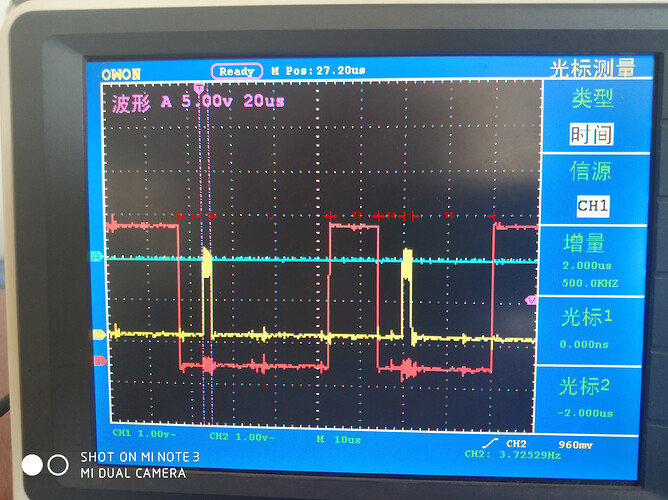

The wave of our SPI is wave.jpg.

The red line is cs,and the yellow line is MOSI.

The T1 is 5.6us,The T2 is 27.6us. T3 is 11.2us. T4 is 5.6us. T5 is 18.4us.

How could I make the T1,T2,T3,T4,T5 as short as possible?

The dts is:

spi@3240000 {

status = "okay";

cs-gpios = <&tegra_main_gpio TEGRA_MAIN_GPIO(N,6) 0>;

spi@0 {

status = "okay";

compatible = "motor";

reg = <0x0>;

spi-max-frequency = <0x1312D00>;

nvidia,enable-hw-based-cs;

nvidia,cs-setup-clk-count = <0x1e>;

nvidia,cs-hold-clk-count = <0x1e>;

nvidia,rx-clk-tap-delay = <0x0>;

nvidia,tx-clk-tap-delay = <0x0>;

nvidia,clk-delay-between-packets = <0x0>;

};

};